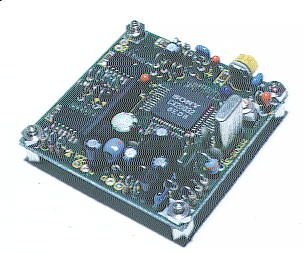

俹俴俴敪怳婍

栚師仺帠椺廤仺挻崅惛搙僨僕僞儖帪寁仺挻崅惛搙僨僕僞儖帪寁偺嶌惉

| 婎弨廃攇悢敪怳婍 | 悈徎敪怳婍側偳埨掕搙偺崅偄敪怳婍傪巊偄傑偡丅 |

| 揹埑惂屼敪怳婍 |

倁俠俷(Voltage Controlled Oscillator) 惂屼梡偺揹埑偱敪怳廃攇悢偑曄傢傞敪怳婍偱偡丅 |

| 埵憡斾妑婍 |

婎弨敪怳廃攇悢偲弌椡廃攇悢傪斾妑偟偰嵎偑偁傞 応崌偵偦偺嵎偵尒崌偆暘偺揹埑傪弌椡偟傑偡丅 弌椡廃攇悢偺曽偑崅偄応崌偵偼VCO偵廃攇悢傪 壓偘傞傛偆側揹埑偑弌椡偝傟傑偡丅 |

| 踢鄹拮咸拶ザ齿腊 |

弌椡廃攇悢傪暘妱偟偰斾妑廃攇悢傪嶌傝傑偡丅 偙偺冻菽抣傪曄偊傞偙偲偵傛傝弌椡廃攇悢傪曄偊傞 偙偲偑偱偒傑偡丅 |

僾儘僌儔儅僽儖僇僂儞僞偺摦嶌

僾儘僌儔儅僽儖僇僂儞僞偺摦嶌

塃偺夞楬恾偼僾儘僌儔儅僽儖僇僂儞僞偺晹暘傪彮偟徻偟偔彂偄偨傕偺偱偡丅

塃偺夞楬恾偼僾儘僌儔儅僽儖僇僂儞僞偺晹暘傪彮偟徻偟偔彂偄偨傕偺偱偡丅